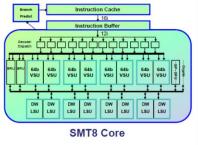

# Optimized for Stronger Thread Performance and Efficiency Increased execution bandwidth efficiency for a range of workloads including commercial, cognitive and analytics Sophisticated instruction scheduling and branch prediction for unoptimized applications and interpretive languages Adaptive features for improved efficiency and performance especially in lower memory bandwidth systems Available with SMT8 or SMT4 Cores 8 or 4 threaded core built from modular execution slices

#### POWER9 SMT8 Core

- · PowerVM Ecosystem Continuity

- · Strongest Thread

- · Optimized for Large Partitions

#### POWER9 SMT4 Core

- Linux Ecosystem FocusCore Count / Socket

- Virtualization Granularity

Source: IBM

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

< 3 >

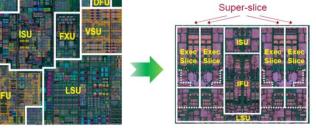

# POWER9 Core Microarchitecture Modular Execution Slices 4 x 128b 2 x 128b 2 x 128b

# Super-slice Super-slice Slice 2 x 128b Super-slice Super-slice Slice Execution Slices 128b 64b Super-slice Slice 150 Slice Slice

<4>

#### **POWER9 SMT4 Core**

#### Re-factored Core Provides Improved Efficiency & Workload Alignment

- · Enhanced pipeline efficiency with modular execution and intelligent pipeline control

- · Increased pipeline utilization with symmetric data-type engines: Fixed, Float, 128b, SIMD

- · Shared compute resource optimizes data-type interchange

Source: IBM

Paderborn

Center for

Parallel

Computing

J. Simon - Architecture of Parallel Computer Systems

**POWER8 SMT8 Core**

SoSe 2018

2

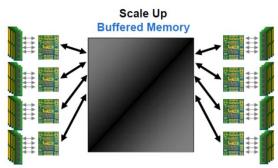

# POWER9 - Dual Memory Subsystem

#### Scale Out Direct Attach Memory

#### 8 Direct DDR4 Ports

- · Up to 120 GB/s of sustained bandwidth

- Low latency access

- Commodity packaging form factor

- Adaptive 64B / 128B reads

#### **8 Buffered Channels**

- · Up to 230GB/s of sustained bandwidth

- Extreme capacity up to 8TB / socket

- Superior RAS with chip kill and lane sparing

- · Compatible with POWER8 system memory

- · Agnostic interface for alternate memory innovations

< 5 >

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

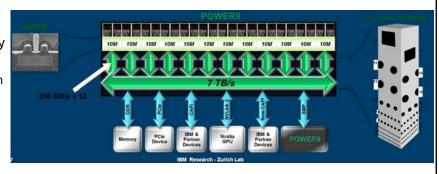

# POWER9 Processor – Common Features

#### **New Core Microarchitecture**

- Stronger thread performance

- · Efficient agile pipeline

- · POWER ISA v3.0

#### **Enhanced Cache Hierarchy**

- 120MB NUCA L3 architecture

- 12 x 20-way associative regions

- · Advanced replacement policies

- · Fed by 7 TB/s on-chip bandwidth

#### Cloud + Virtualization Innovation

- · Quality of service assists

- · New interrupt architecture

- · Workload optimized frequency

- · Hardware enforced trusted execution

# SMP/Accelerator Signaling Memory Signaling Gore Core Gore Core 12 12 13 Region 13 Region

#### 14nm finFET Semiconductor Process

- Improved device performance and reduced energy

- · 17 layer metal stack and eDRAM

- · 8.0 billion transistors

#### Leadership Hardware Acceleration Platform

- Enhanced on-chip acceleration

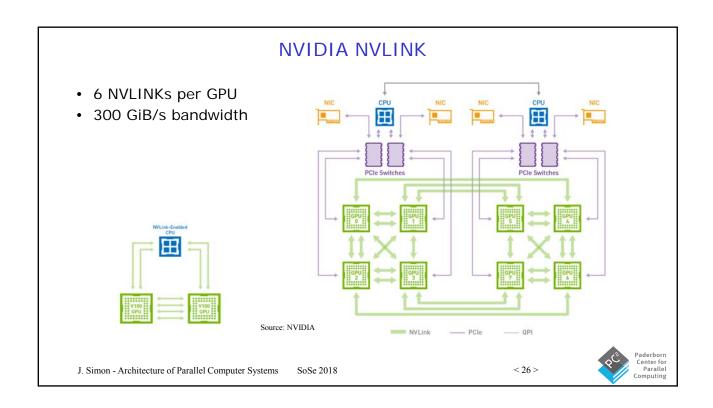

- Nvidia NVLink 2.0: High bandwidth and advanced new features (25G)

- CAPI 2.0: Coherent accelerator and storage attach (PCIe G4)

- New CAPI: Improved latency and bandwidth, open interface (25G)

#### State of the Art I/O Subsystem

· PCle Gen4 - 48 lanes

#### High Bandwidth Signaling Technology

- · 16 Gb/s interface

- Local SMP

- · 25 Gb/s Common Link interface

- Accelerator, remote SMP

Source: IBM

Paderborn

Center for

Parallel

Computing

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

< 6 >

# POWER9 Data Capacity & Throughput

#### L3 Cache

- · 120 MB shared capacity

- Per 2x Core

- 10 MB L3 cache region

- 512 kB L2 cache

<7>

#### High-throughput on-chip fabric

- Over 7 TB/s on-chip switch

- · Move data in/out at 256 GB/s per 2x Core

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

#### POWER9 - Scale Out Family L922 S922 S914 S924 H922 H924 9008-22L 9009-22A 9009-41A 9009-42A 9223-22H 9223-42H • 1,2-socket, 2U • 1,2-socket, 2U • 1-socket, 4U & · 2-socket, 4U • 1.2-socket, 2U · 2-socket, 4U • 8,10,12 cores/skt • 4, 8,10 cores/skt Tower • 8,10,12 cores/skt • 4, 8,10 cores/skt • 8,10,12 cores/skt • 32 IS DIMM slots • 32 IS DIMM slots • 4,6,8 cores/skt • 32 IS DIMM slots • 32 IS DIMM slots • 32 IS DIMM slots 4TB memory 4TB memory • 16 IS DIMM slots 4TB memory 4TB memory 4TB memory • 4 CAPI 2.0 Slots • 1TB memory • 2 CAPI 2.0 Slots Internal RDX Media • Internal RDX Media • Internal RDX Media • AIX, IBM i, Linux • AIX, IBM i, Linux • AIX, IBM i Linux only • AIX, IBM i, & Linux • PowerVM • AIX, IBM i up to 25% PowerVM PowerVM • PowerVM up to 25% • Linux • PowerVM KVM (GA2) Linux PowerVM **FAMILY FEATURES** Cloud enabled - Embedded virtualization capabilities with PowerVM DDR4 Industry Standard (IS) memory RDIMMs High Speed 25Gb/s external ports - one per socket 2 Internal NVMe Flash boot adapters Embedded Analytics and Algorithms on the chip help run POWER9 at an always optimized frequency No internal DVD Drive Source: IBM Paderborn Center for Parallel

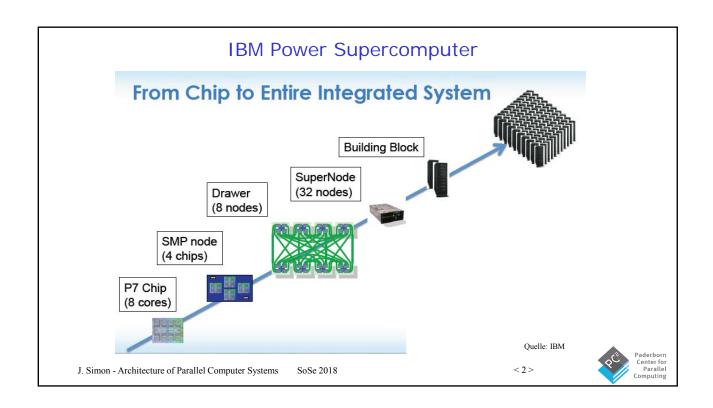

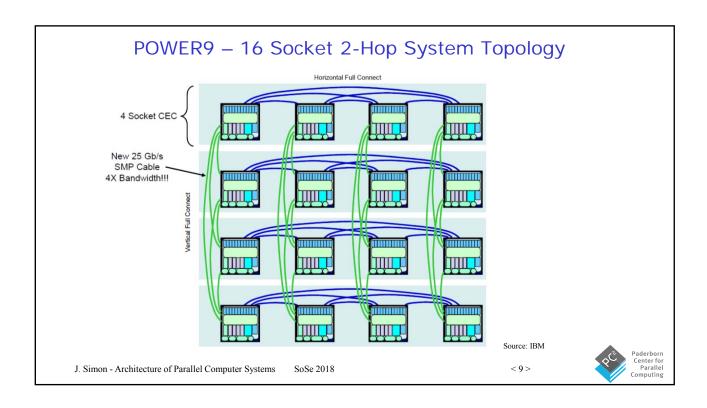

# **Interconnection Network**

- HUB/Switch (one per SMP node)

- 192 GB/s to host node

- 336 GB/s to 7 other nodes in same drawer

- 240 GB/s to 24 nodes in other 3 drawers in same SuperNode

- 320 GB/s to hubs in other SuperNodes

< 10 >

Source: IBM

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

Paderborn Center for Parallel Computing

5

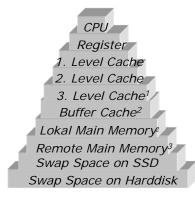

# Memory Hierarchy: Example IBM Power E870 (Power8)

| Kapazität  | Bandbreite      | Latenz  |

|------------|-----------------|---------|

| 256 Byte   | 120 GByte/s     | 0.2 ns  |

| 64 kByte   | 75 GByte/s      | 1 ns    |

| 512 kByte  | 150 GByte/s     | 4 ns    |

| 80 MByte   | 150 GByte/s     | < 30 ns |

| 128 Mbyte  | ?               | ?       |

| 1024 GByte | 230 GByte/s     | < 90 ns |

| 8192 GByte | 230 GByte/s     | < 1 μs  |

| >          | X * 500 MByte/s | < 1 ms  |

| >>         | X * 200 MByte/s | ~5 ms   |

- <sup>1</sup> 8MB per Core x 10

- shared by 10 Cores

shared by 80 Cores

< 11 >

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

### POWER9 - Acceleration

# PCIe Gen3 x16

# PCIe Gen4 x16

# POWER8 with NVLink 1.0

#### Increased Performance / Features / Acceleration Opportunity

#### Extreme Accelerator Bandwidth and **Reducend Latencys**

- PCIe Gen 4 x 48 lanes 192 GB/s peak bandwidth

- IBM BlueLink 25 Gb/s x 48 lanes 300 GB/s peak bandwidth

# Coherent Memory and Virtual Addressing Capability for all Accelerators

- CAPI 2.0 using PCIe Gen 4

- NVLink 2.0 next generation of GPU/CPU bandwidth and integration usinmg BLueLink

- OpenCAPI openinterface with high bandwidth and low latency using BlueLink

Source: IBM Paderborn Center for

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

< 12 >

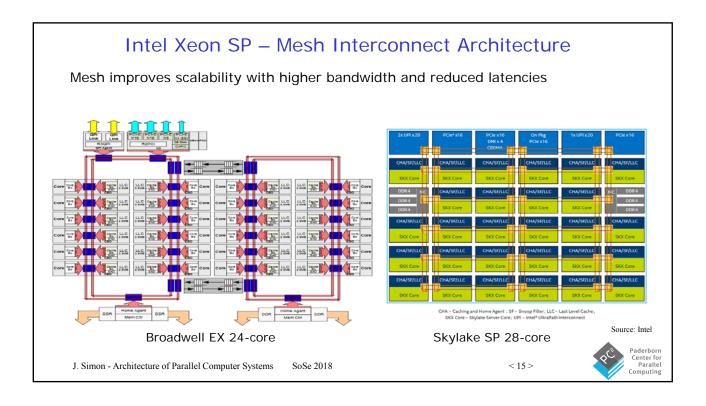

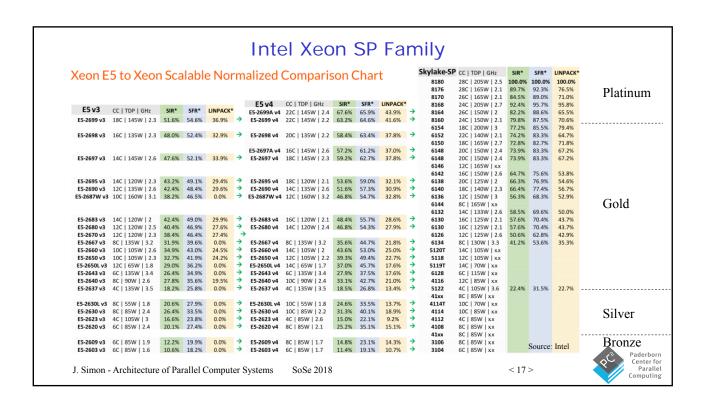

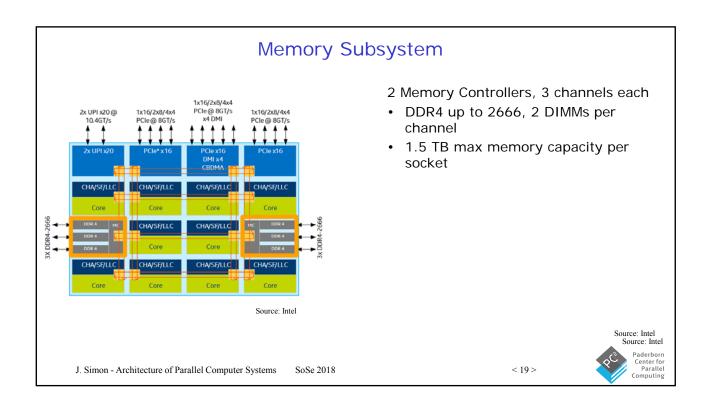

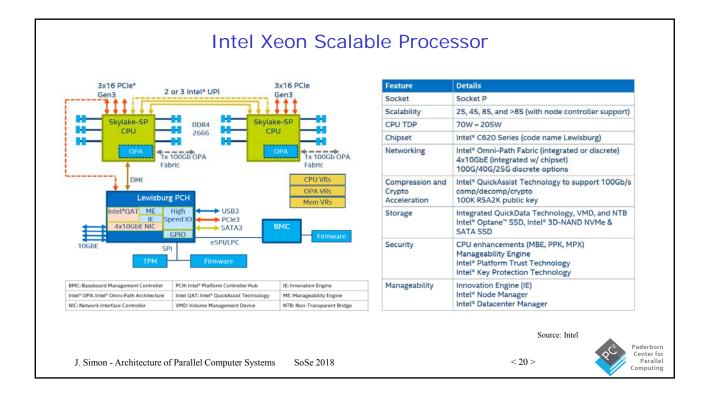

# Example: Intel Xeon "Skylake"

- AVX-512 64 Single-Precision FLOP/s or 32 Double-Precision FLOP/s

- Ultra Path Interconnect (UPI) with 10.4 Gigatransfers per second (GT/s)

| Features                                | Intel® Xeon® Processor E5-2600 v4                        | Intel® Xeon® Scalable Processor                          |  |

|-----------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--|

| Cores Per Socket                        | Up to 22                                                 | Up to 28                                                 |  |

| Threads Per Socket                      | Up to 44 threads                                         | ds Up to 56 threads                                      |  |

| Last-level Cache (LLC)                  | Up to 55 MB                                              | Up to 38.5 MB (non-inclusive)                            |  |

| QPI/UPI Speed (GT/s)                    | 2x QPI channels @ 9.6 GT/s                               | Up to 3x UPI @ 10.4 GT/s                                 |  |

| PCIe* Lanes/<br>Controllers/Speed(GT/s) | 40 / 10 / PCle* 3.0 (2.5, 5, 8 GT/s)                     | 48 / 12 / PCle 3.0 (2.5, 5, 8 GT/s)                      |  |

| Memory Population                       | 4 channels of up to 3 RDIMMs,<br>LRDIMMs, or 3DS LRDIMMs | 6 channels of up to 2 RDIMMs,<br>LRDIMMs, or 3DS LRDIMMs |  |

| Max Memory Speed                        | Up to 2400                                               | Up to 2666                                               |  |

| TDP (W)                                 | 55W-145W                                                 | 70W-205W                                                 |  |

Source: Intel

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 14 >

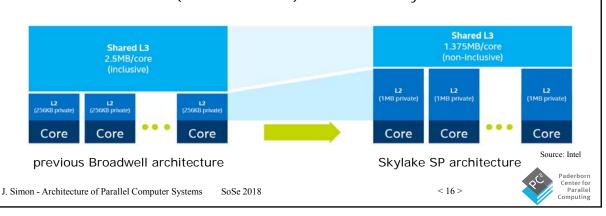

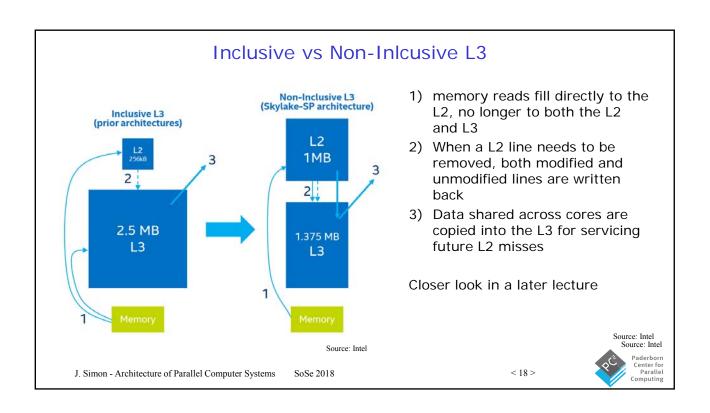

# Intel Xeon SP – Cache Hierarchy

#### On-chip cache

- · Processor core with

- 640 KiB L1 data cache and 640 KiB L1 instruction cache (both 8-way set associative)

- 1 MiB L2 cache (16-way set associative)

- private L2 becomes primary cache with shared L3 used as overflow cache

- Non-inclusive L3 cache (1.375 MiB / core) lines in L2 may not exist in L3

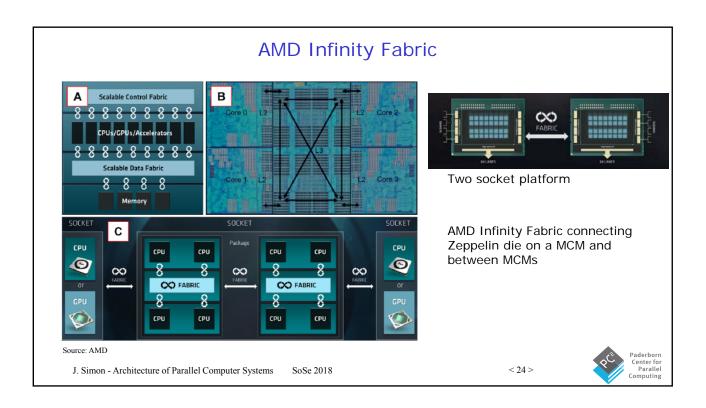

- ZEN Microarchitecture

- L1 D-cache with 32 kiB, 8 way

- L1 I-cache with 64 kiB, 4 way

- L2 cache with 512 kiB, 8 way

- CPU Complex

- Four cores connected to an L3 cache

- L3 cache with 8 MiB, 16 way associative

- Multi chip processors

- Four CCX per processor

- · Infinity Fabric

- 42 GiB/s bi-directional bandwidth per link

- Fully connected coherent Infinity Fabric within socket

- Dual socket systems with two processors connected with 4 x 38 GiB/s links

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

# CPU Complex

#### Multi Chip processor

< 22 >

# AMD Epyc 7000 Series

- AMD EPYC 7601

- 32 Cores, 2.2 GHz (max boost clock 3.2 GHz, all cores max boost 2.7 GHz)

- 64 MiB L3-cache

- TDP 180 Watt

- 1 or 2 sockets

- AMD EPYC 7451

- 24 cores, 2.3 GHz (max boost clock 3.2 GHz)

- TDP 180 Watt

- 1 or 2 sockets

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 23 >

# Example: NVIDIA Stream Processor (GPU) NVIDIA Tesla V100 21 billion transistors 80 SM stream multiprocessors - 5,120 CUDA Cores - 1.45 GHz - 6 MiB shared L2 cache 640 tensor cores - Accelerates Deep learning applications Main memory - 16 GiB HBM2 (High-Source: NVIDIA Bandwidth-Memory) 7.5 TFLOPS DP, 15 TFLOPS SP - 900 GiB/s NVLINK Training, Inference: 120 TOPS

SoSe 2018

< 25 >

J. Simon - Architecture of Parallel Computer Systems

# Accelerators become part of the Processor

- Floating-Point Unit

- 1978: Intel 8086 + Intel 8087 Math-Co processor (16 Bit)

- 1989: Intel i486 with integrated floating-point units (32 bit)

- Vector Unit

- 1993: CM5 with Sparc processor + Vector Unit Accelerators (MBUS)

- 1995: Intel Pentium P55C with MMX instructions

- 1996: Motorola PowerPC with AltiVec

- Stream Processing

- 2006: Workstation + GPU graphic card (PCI)

- 2011: Intel HD Graphics 3000 with integrated GPU (OpenCL)

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 27 >

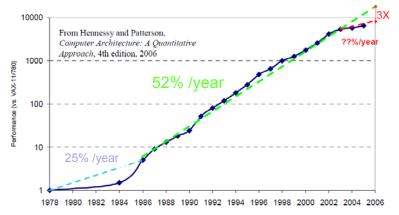

# Leistungsentwicklung eines Prozessorkerns

- Von 1986 bis 2002 ca. 50% Leistungszuwachs pro Jahr

- · Derzeit Einzelprozessorleistung nur langsam zunehmend

- Höherer Leistungszuwachs nur noch über Erhöhung der Anzahl an Prozessoren (Cores) möglich

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 28 >

# Memory Bandwidth/Latency

| Generation    | Туре      | Peak Bandwidth | Latency<br>(1st word) |

|---------------|-----------|----------------|-----------------------|

| SDRAM (1990s) | PC-100    | 0.8 Gbyte/s    | 20 ns                 |

| DDR (2000)    | DDR-200   | 1.6 Gbyte/s    | 20 ns                 |

| DDR           | DDR-400   | 3.2 Gbyte/s    | 15 ns                 |

| DDR2 (2003)   | DDR2-667  | 5.3 Gbyte/s    | 15 ns                 |

| DDR2          | DDR2-800  | 6.4 Gbyte/s    | 15 ns                 |

| DDR3 (2007)   | DDR3-1066 | 8.5 Gbyte/s    | 13 ns                 |

| DDR3          | DDR3-1600 | 12.8 Gbyte/s   | 11.25 ns              |

| DDR4 (2014)   | DDR4-2133 | 17 Gbyte/s     | ~ 11 ns               |

| DDR4          | DDR4-2666 | 21 Gbyte/s     | ~10.5 ns              |

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

Paderborn Center for Parallel Computing

< 30 >

15

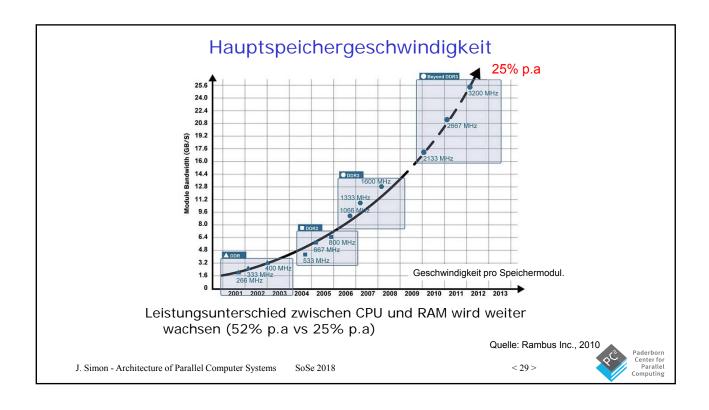

# **Trends**

- "Power Wall"

- Energieaufnahme / Kühlung

- Lösungen

- geringere Taktfrequenzen

- mehr Ausführungseinheiten

- "Memory Wall"

- Speicherbandbreite u. Latenz

- Lösungen

- bessere Speicherhierarchien u. Anbindung an CPUs

- · Latency-Hidding

- "ILP Wall"

- Beschränkte Parallelität im sequentiellen Instruktionsstrom

- Lösungen

- mehr Parallelität in Programmen erkennen (Compiler)

- mehr explizite Parallelität in Programmen (Programmiersprachen)

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 31 >

< 32 >

# Architekturen paralleler Rechnersysteme

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

Paderborn Center for Parallel Computing

# Einfache Definition Parallelrechner

George S. Almasi, *IBM Thomas J. Watson Research Center* Allan Gottlieb, *New York University*, 1989

" A parallel computer is a collection of processing elements that communicate and cooperate to solve large problems fast."

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

< 33 >

# Rechnerarchitektur allgemein

Eine Rechnerarchitektur ist bestimmt durch ein Operationsprinzip für die Hardware und die Struktur ihres Aufbaus aus den einzelnen Hardware-Betriebsmitteln

(Giloi 1993)

#### Operationsprinzip

Das Operationsprinzip definiert das funktionelle Verhalten der Architektur durch Festlegung einer Informationsstruktur und einer Kontrollstruktur.

#### Hardware-Struktur

Die Struktur einer Rechnerarchitektur ist gegeben durch Art und Anzahl der Hardware-Betriebsmittel und deren verbindenden Kommunikationseinrichtungen.

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 34 >

# ... in anderen Worten

# Operationsprinzip

Vorschrift über das Zusammenspiel der Komponenten

#### Struktur

- Einzelkomponenten und deren Verknüpfung

- Grundlegende Strukturbausteine sind

- Prozessor (CPU), als aktive Komponente zur Ausführung von Programmen,

- Hauptspeicher (ggf. hierarchisch strukturiert, ...),

- Übertragungsmedium zur Verbindung der einzelnen Architekturkomponenten,

- Steuereinheiten für Anschluss und Kontrolle von Peripherie-geräten und

- Geräte, als Zusatzkomponenten für Ein- und Ausgabe von Daten sowie Datenspeicherung.

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

< 35 >

< 36 >

### Parallelrechner

- Operationsprinzip:

- gleichzeitige Ausführung von Befehlen

- sequentielle Verarbeitung in bestimmbaren Bereichen

- Arten des Parallelismus:

- Explizit: Die Möglichkeit der Parallelverarbeitung wird a priori festgelegt. Hierzu sind geeignete Datentypen bzw. Datenstrukturen erforderlich, z.B. Vektoren (lineare Felder) samt Vektoroperationen.

- Implizit: Die Möglichkeit der Parallelverarbeitung ist nicht a priori bekannt. Durch eine Datenabhängigkeitsanalyse werden die parallelen und sequentiellen Teilschritte des Algorithmus zur Laufzeit ermittelt.

Paderborn Center for Paralle Computing

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

#### Strukturelemente von Parallelrechnern

- Parallelrechner besteht aus einer Menge von Verarbeitungselementen, die in einer koordinierten Weise, teilweise zeitgleich, zusammenarbeiten, um eine Aufgabe zu lösen

- · Verarbeitungselemente können sein:

- spezialisierte Einheiten, wie z.B. die Pipeline-Stufen eines Skalarprozessors oder die Vektor-Pipelines der Vektoreinheit eines Vektorrechners

- gleichartige Rechenwerke, wie z.B. die Verarbeitungselemente eines Feldrechners

- Prozessorknoten eines Multiprozessorsystems

- vollständige Rechner, wie z.B. Workstations oder PCs eines Clusters

- selbst wieder ganze Parallelrechner oder Cluster

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 37 >

< 38 >

### Grenzbereiche von Parallelrechnern

- eingebettete Systeme als spezialisierte Parallelrechner

- Superskalar-Prozessoren, die feinkörnige Parallelität durch Befehls-Pipelining und Superskalar-Technik nutzen

- Mikroprozessoren arbeiten als Hauptprozessor teilweise gleichzeitig zu einer Vielzahl von spezialisierten Einheiten wie der Bussteuerung, DMA-,Graphikeinheit, usw.

- Ein-Chip-Multiprozessor

- mehrfädige (multithreaded) Prozessoren führen mehrere Kontrollfäden überlappt oder simultan innerhalb eines Prozessors aus

- VLIW- (Very Long Instruction Word)- Prozessor

Paderborn Center for Parallel Computing

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

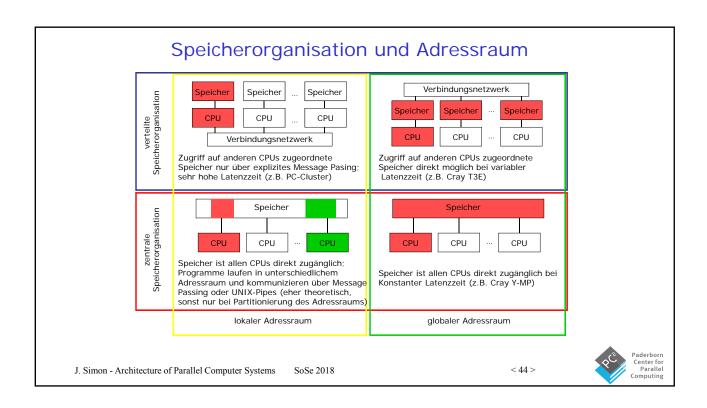

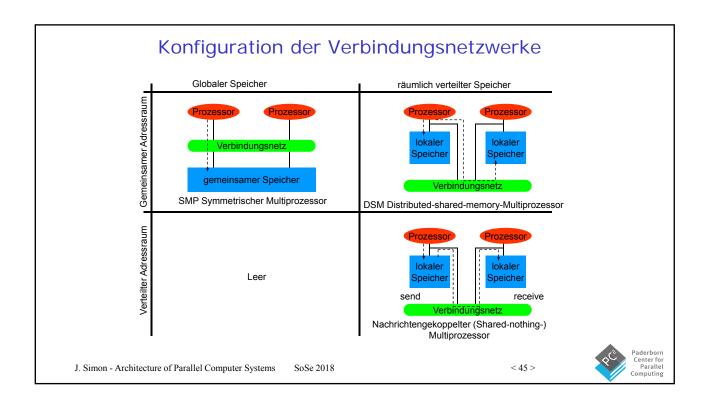

# Klassifikation von Parallelrechnern

- Klassifikation nach Flynn, d.h. Klassifikation nach der Art der Befehlsausführung

- Klassifikation nach der Speicherorganisation und dem Adressraum

- Konfigurationen des Verbindungsnetzwerks

- · Varianten an speichergekoppelte Multiprozessorsysteme

- · Varianten an nachrichtengekoppelte Multiprozessorsysteme

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

< 39 >

Paderborn Center for Parallel Computing

# Klassifikation nach Flynn

Zweidimensionale Klassifizierung mit Kriterium Anzahl der Befehls- und Datenströme

- Rechner bearbeitet zu einem Zeitpunkt einen oder mehrere Befehle

- Rechner bearbeitet zu einem Zeitpunkt einen oder mehrere Datenwerte

- ⇒ Damit vier Klassen von Rechnerarchitekturen

- SISD: Single Instruction, Single Data

Ein Befehl verarbeitet einen Datensatz. (herkömmliche Rechnerarchitektur eines seriellen Rechners)

- SIMD: Single Instruction, Multiple Data

Ein Befehl verarbeitet mehrere Datensätze, z.B. N Prozessoren führen zu einem Zeitpunkt den gleichen Befehl aber mit unterschiedlichen Daten aus.

- MISD: Multiple Instruction, Single Data

Mehrere Befehle verarbeiten den gleichen Datensatz. (Diese Rechnerarchitektur ist nie realisiert worden.)

- MIMD: Multiple Instruction, Multiple Data

Unterschiedliche Befehle verarbeiten unterschiedliche Datensätze.

(Dies ist das Konzept fast aller modernen Parallelrechner.)

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 40 >

# SISD Architektur

Klassische Struktur eines seriellen Rechners: Nacheinander werden verschiedene Befehle ausgeführt, die z.B. einzelne Datenpaare verknüpfen

- Moderne RISC (Reduced Instruction Set Computer) Prozessoren verwenden Pipelining:

- Mehrere Funktionseinheiten, die gleichzeitig aktiv sind.

- Operationen sind in Teiloperationen unterteilt.

- In jedem Takt kann eine Funktionseinheit (z.B. Addititionseinheit) eine neue Operation beginnen.

- D.h. hohe interne Parallelität nutzbar

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 41 >

< 42 >

# SIMD Architektur (Prozessorarray)

- Mehrere Prozessoren führen zu einem Zeitpunkt den gleichen Befehl aus

- Rechner für Spezialanwendungen (z.B. Bildverarbeitung, Spracherkennung)

- I.A. sehr viele Prozessorkerne (tausende Kerne in einem System)

- · Beispiele: Graphikprozessoren, Numerische Coprozessoren

· Mittlerweile auch innerhalb einzelner Funktionseinheiten zu finden

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

Paderborn Center for Parallel Computing

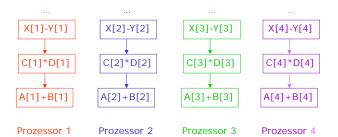

#### MIMD Architektur Mehrere Prozessoren führen unabhängig voneinander unterschiedliche Instruktionen auf unterschiedlichen Daten aus: do i = 1,nt = 1/xa(i)=b(i) z=a(i)call sub call sub1 x=a(1)/tend do x = yn=100 b=0.d0 $T = \sin(r)$ Prozessor 1 Prozessor 2 Prozessor 3 Prozessor 4 Fast alle aktuellen Systeme entsprechen dieser Architektur.

SoSe 2018

J. Simon - Architecture of Parallel Computer Systems

< 43 >

# Arten von Multiprozessorsystemen

- Bei speichergekoppelten Multiprozessorsystemen besitzen alle Prozessoren <u>einen</u> gemeinsamen Adressraum.

Kommunikation und Synchronisation geschehen über gemeinsame Variablen.

- symmetrisches Multiprozessorsystem (SMP): ein globaler Speicher

- Distributed-Shared-Memory-System (DSM): gemeinsamer Adressraum trotz räumlich verteilter Speichermodule

- Beim nachrichtengekoppelten Multiprozessorsystem besitzen alle Prozessoren nur räumlich verteilte Speicher und prozessorlokale Adressräume.

Die Kommunikation geschieht durch Austausch von Nachrichten.

- Massively Parallel Processors (MPP), eng gekoppelte Prozessoren

- Verteiltes Rechnen in einem Workstation-Cluster.

- Grid-/Cloud-Computing: Zusammenschluss weit entfernter Rechner

< 46 >

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

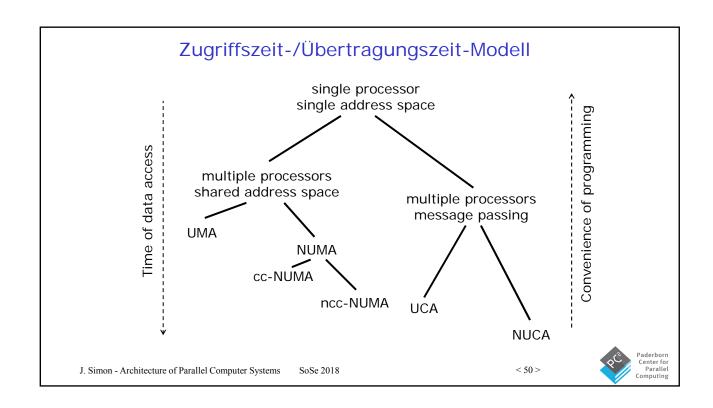

# Speichergekoppelte Multiprozessorsysteme

- Alle Prozessoren besitzen einen gemeinsamen Adressraum; Kommunikation und Synchronisation geschieht über gemeinsame Variablen.

- Uniform-Memory-Access-Modell (UMA):

- Alle Prozessoren greifen in gleichermaßen auf einen gemeinsamen Speicher zu. Insbesondere ist die Zugriffszeit aller Prozessoren auf den gemeinsamen Speicher gleich. Jeder Prozessor kann zusätzlich einen lokalen Cache-Speicher besitzen. Typische Beispiel: die symmetrischen Multiprossorsysteme (SMP)

- Nonuniform-Memory-Access-Modell (NUMA):

- Die Zugriffszeiten auf Speicherzellen des gemeinsamen Speichers variieren je nach dem Ort, an dem sich die Speicherzelle befindet. Die Speichermodule des gemeinsamen Speichers sind physisch auf die Prozessoren aufgeteilt.

- Typische Beispiele: Distributed-Shared-Memory-Systeme.

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 47 >

< 48 >

# Nachrichtengekoppelte Multiprozessorsysteme

- **Uniform-Communication-Architecture-ModelI** (UCA): Zwischen allen Prozessoren können gleich lange Nachrichten mit einheitlicher Übertragungszeit geschickt werden.

- Non-Uniform-Communication-Architecture-Modell (NUCA): Die Übertragungszeit des Nachrichtentransfers zwischen den Prozessoren ist je nach Sender- und Empfänger-Prozessor unterschiedlich lang.

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

# Speicher- vs. Nachrichtenkopplung

- Distributed-Shared-Memory-Systeme sind NUMAs: Die Zugriffszeiten auf Speicherzellen des gemeinsamen Speichers variieren je nach Ort, an dem sich die Speicherzelle befindet.

- cc-NUMA (Cache-coherent NUMA): Cache-Kohärenz wird über das gesamte System gewährleistet, z.B. SGI Origin, HP Superdome, IBM Regatta

- ncc-NUMA (Non-Cache-coherent NUMA): Cache-Kohärenz wird nur innerhalb eines Knoten gewährleistet, z.B. Cray T3E, SCI-Cluster

- COMA (Cache-only-Memory-Architecture): Der Speicher des gesamten Rechners besteht nur aus Cache-Speicher. Nur in einem kommerziellen System realisiert (ehemalige Firma KSR)

- Nachrichten gekoppelte Multiprozessorsysteme sind NORMAs (Noremote-memory-access-Modell) oder Shared-nothing-Systeme, z.B. IBM SP, HP Alpha Cluster

J. Simon - Architecture of Parallel Computer Systems SoS

SoSe 2018

< 49 >

# Zusammenfassung: Klassifizierung

# Klassifizierung nach

- Befehls- und Datenströme,

- · Speicherorganisation,

- Verbindungsnetzwerk

- weitere Details später in der Vorlesung

J. Simon - Architecture of Parallel Computer Systems

SoSe 2018

< 51 >

# Quantitative Bewertung von Parallelrechnern

Merkmale: Geschwindigkeit, Auslastung

- Ausführungszeit T eines parallelen Programms

- Zeit zwischen dem Starten der Programmausführung auf einem der Prozessoren bis zu dem Zeitpunkt, an dem der letzte Prozessor die Arbeit an dem Programm beendet hat

- Während der Programmausführung sind alle Prozessoren in einem von drei Zuständen

- rechnend

- kommunizierend

- untätig

J. Simon - Architecture of Parallel Computer Systems SoSe 2018 < 52 >

# Ausführungszeit T

Ausführungszeit T eines parallelen Programms auf einem dediziert zugeordneten Parallelrechner setzt sich zusammen aus:

- Berechnungszeit T<sub>comp</sub>

- Zeit für die Ausführung von Rechenoperationen

- Kommunikationszeit Tcom

- Zeit für Sende- und Empfangsoperationen

- Untätigkeitszeit T<sub>idle</sub>

- Zeit für Warten (auf zu empfangende oder zu sendende Nachrichten)

Es gilt:  $T \approx T_{comp} + T_{com} + T_{idle}$

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 53 >

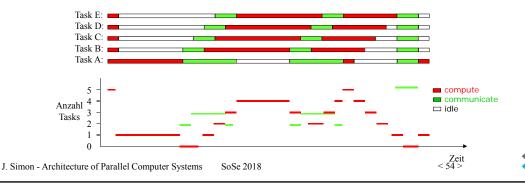

# Parallelitätsprofil

- Parallelitätsprofil zeigt die vorhandene Parallelität in einem parallelen Programm (einer konkreten Ausführung)

- Grafische Darstellung:

Auf der x-Achse wird die Zeit und auf der y-Achse die Anzahl paralleler Aktivitäten aufgetragen.

- Perioden von Berechnungs- Kommunikations- und Untätigkeitszeiten sind erkennbar.

Paderborn Center for Parallel Computing

# Beschleunigung und Effizienz

- Beschleunigung (Leistungssteigerung, Speedup):  $S(n) = \frac{T(1)}{T(n)}$

- Effizienz:  $E(n) = \frac{S(n)}{n}$

- T(1) Ausführungszeit auf einem Einprozessorsystem

- T(n) Ausführungszeit auf einem System mit n Prozessoren

Die "Zeit" ist auch in Schritte oder Takte messbar.

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 55 >

## Skalierbarkeit

#### Skalierbarkeit eines Parallelrechners

- Das Hinzufügen von weiteren Verarbeitungselementen führt zu einer kürzeren Gesamtausführungszeit, ohne dass das Programm geändert werden muss.

- Wichtig für die Skalierbarkeit sind jeweils angemessene Problemgrößen.

- Bei fester Problemgröße und steigender Prozessorzahl wird ab einer bestimmten Prozessorzahl eine Sättigung eintreten. Die Skalierbarkeit ist in jedem Fall beschränkt (*strong scaling*).

- Darf mit Anzahl an Prozessoren auch die Problemgröße steigen (*weak scaling*), dann muss ein skalierendes Hardware- und Software-System den Sättigungseffekt nicht aufweisen.

#### Gute Skalierbarkeit:

Lineare Steigerung der Beschleunigung mit einer Effizienz nahe Eins.

J. Simon - Architecture of Parallel Computer Systems SoSe 2018

< 56 >