### OpenCL Design Flows for Intel and Xilinx FPGAs

Common Optimization Strategies, Design Patterns and Vendor-specific Differences

#### **Tobias Kenter**

Paderborn Center for Parallel Computing & Department of Computer Science Paderborn University, Germany

DATE, Monday Tutorials – 25 March 2019 – Florence, Italy

# Part 1 Common Design Patterns Key Differences

# Introduction

# My Agenda

• Our mission at PC<sup>2</sup>

Promote and Establish FPGAs as accelerators in HPC

Paderborn Center for Parallel Computing

• Objectives for applications and libraries

Achieve Throughput Close to Architectural Limits

Use OpenCL as Performance Portable FPGA Design Tool

• How far can those coexist?

# **My Background**

- Research interests / background

- application acceleration

- architecture exploration

- compilation tools

- tool user: OpenCL, Maxeler

- compiler extensions: LLVM, Clang

- Experience with OpenCL FPGA tool chains since 2016

- FDTD stencil computations with Xilinx and Intel

- DG code with Intel

- matrix multiplication with Intel and Xilinx

- CNN, convolutions with Xilinx and Intel

- FFT with Intel

- image processing and generalization with Xilinx

- elliptic curve method with Xilinx

- external channel communication with Intel

### **My Biases**

- Currently more focus on Intel tools due to our hardware setup

- Xilinx SDAccel has an extensive GUI that I mostly ignore here

- makefile + command line flow to quickly switch targets

| Cr Brern tro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                       |                                                                                  | Quick Access             | 9   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------|-----|

| 🖕 Project Explorer 😫 👘 🗖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ≪vscale1_vec ಔ @ kml_vadd.cl @ vscale1_vec.cl D macros.h                                                                                                                                                                                                              |                                                                                  |                          | - 1 |

| - 🕸 🖮 📍                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SDx Application Project Settings                                                                                                                                                                                                                                      | Active build con                                                                 | figuration: Emulation-SW | 4   |

| Solution States Stat | General                                                                                                                                                                                                                                                               | Options                                                                          |                          |     |

| <ul> <li>Èsdx</li> <li>ÈEmulation-HW</li> <li>ÈEmulation-SW</li> <li>Èsrc</li> <li>Èsrn[vadd.cl</li> <li>Èsmacros.h</li> <li>Èsvadd.cpp</li> <li>Èvadd.h</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Project name:       vscale1_vec         Project flow:       SDAccel         Platform:       alpha-data_adm-pcie-8k5_dynamic_5_0         Runtime:       OpenCL         System configuration:       Linux         Number of devices:       1         Hardware Functions | Target:<br>Host debug:<br>Kernel debug:<br>Report type:<br>Hun warm opt materian | Software Emulation       | × × |

| <ul> <li>✓ scale1_vec.cl</li> <li>✓ scl.cpp</li> <li>✓ scl.h</li> <li>✓ Export_Compliance_Notice.md</li> <li>✓ System</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Name Compute Units Port Data Width                                                                                                                                                                                                                                    | Max Mem                                                                          |                          |     |

| Assistant 🛙 🖛                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                       | P D Tarnet Connect                                                               | i 📮 Emulation Cons 🛙     |     |

| <pre>vscale1_vec [OpenCL] C Emulation-SW [Software Emulation C binary_container_1 Vscale [OpenCL] C Emulation-HW [Hardware Emulation System [Hardware]</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDx Build Console [vscale1_vec, Emulation-SW]<br>Attempting to get a License: ap openci<br>INFO: [XOCC 17-1540] The version limit for your license is '2018                                                                                                           | 3.12<br>5 X04                                                                    |                          | 0   |

### **Outline Part 1**

- Overview FPGAs and Goals

- OpenCL Overview

- Example 1: Vector Scale

- compilation

- reports

- performance analysis

- Vector Scale Variations

- automatic unrolling

- Example 2: SAXPY

- blockwise design pattern

- Outer Loop Pipelining

- Streaming Kernels

# **Overview: FPGAs and Goals**

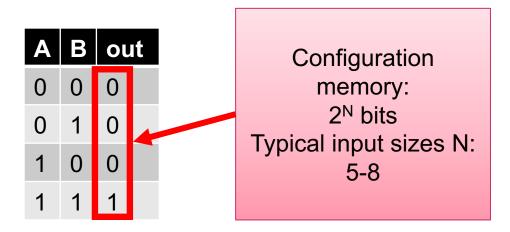

- Field-programmable Gate Array

- Gates

- fundamental building blocks are logic gates

- in all current FPGAs: LUTs (Lookup Tables)

- truth table stored in SRAM

- Array

- many gates (LUTs) in a regular 2D structure

- Field-programmable

- configuration can be changed "in the field", many times

- in practice: currently takes up to few 100 ms

- faster alternatives possible

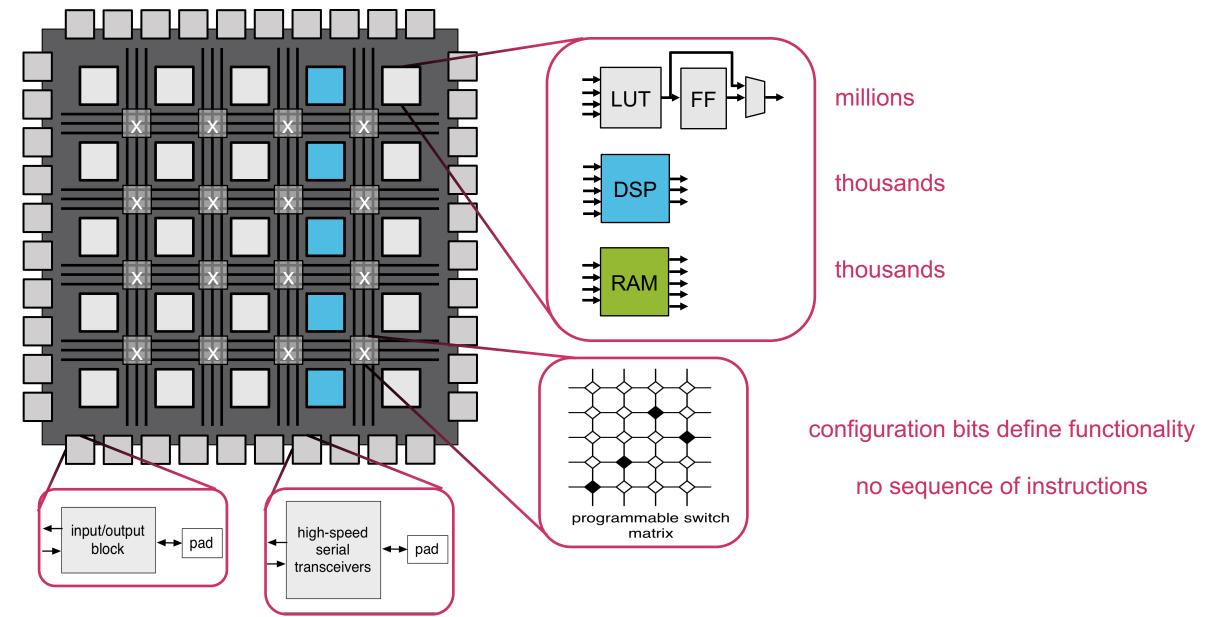

### **FPGA – Basic Structures**

## **FPGA – Configuration and Application Domains**

- configuration

- all FPGAs components are programmable (logic cell, DSP, IO-block functions, routing, ...)

- configuration data (bitstream) is stored in SRAM cells

- bitstream loaded from non-volatile memory at boot time

- some devices can be re-configured at runtime

- application domains

- glue logic

- rapid prototyping, emulation

- embedded systems

- configurable system-on-chip

- ASIC replacement

- reconfigurable computing

- computing without CPUs

- combine processor-like programmability with ASIC-like performance

- recent hot topic: CNNs with customized precision

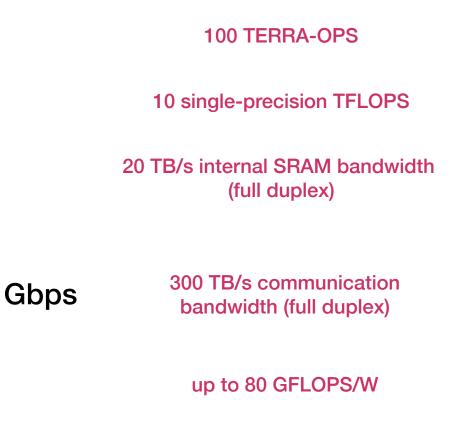

# **FPGA Technology Today**

#### Example: Intel Stratix 10 GX2800 FPGA

- > 900000 configurable logic blocks

- up to 4 Boolean functions of 8 inputs

- 5760 hardened arithmetic units (DSP)

- fixed point and IEEE 754 SP floating-point

- 11721 independent SRAM blocks

- width/depth/ports highly configurable

- integrated DDR4 memory controllers

- up to 96 serial transceivers, up to 28.3 Gbps

- typically about 300-600MHz

- power consumption 50-225W

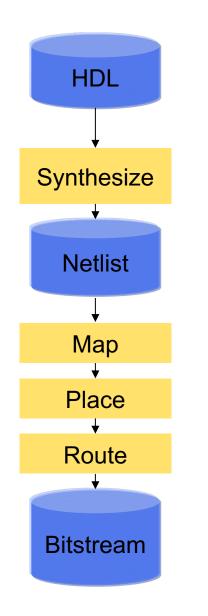

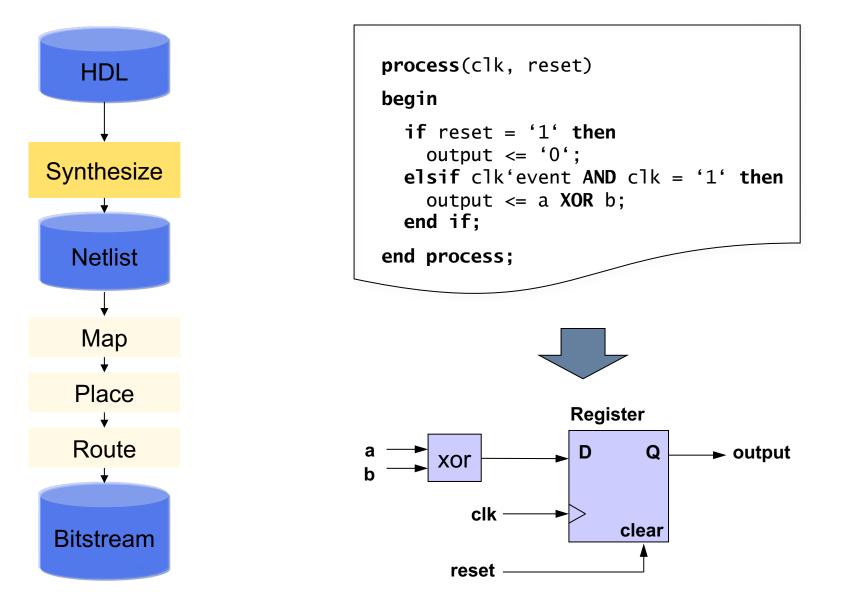

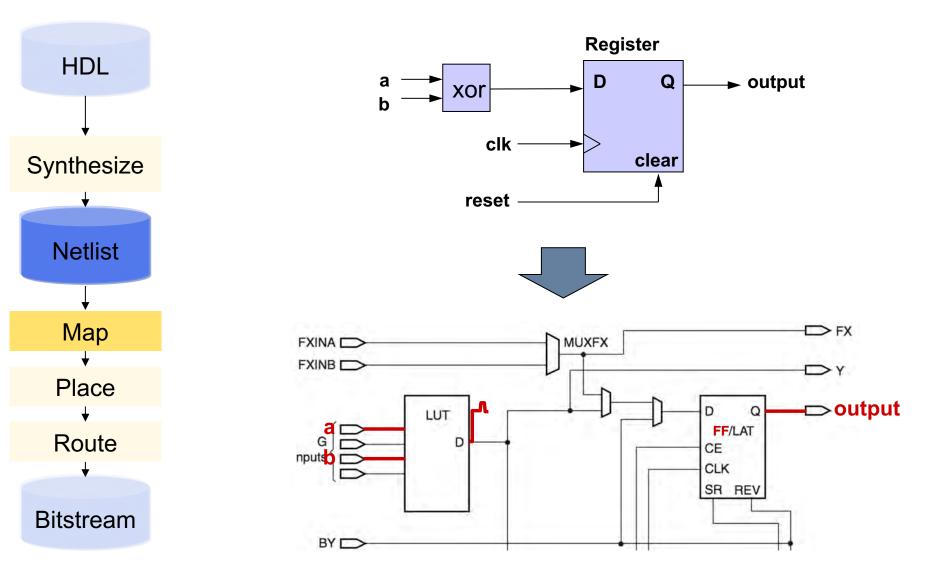

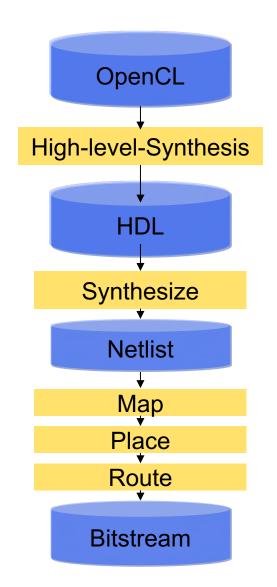

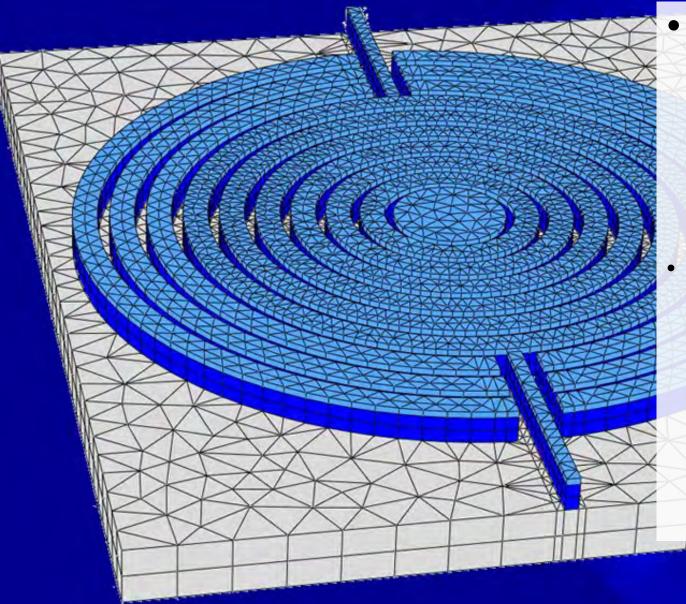

# **Classical FPGA Development**

- Hardware design is traditionally done by modeling the system in a hardware description language (e.g. VHDL or Verilog)

- An FPGA synthesis tool (compiler) generates an netlist of basic logic elements,

- which is then translated (mapped) to components available on the FPGA,

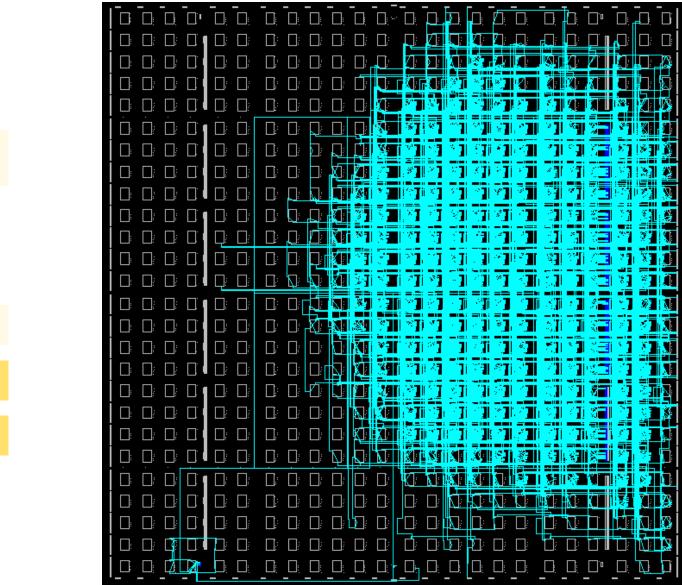

- which are placed on the chip,

- and the connecting signals are routed through the interconnection network.

- The resulting configuration data (bitstream) for programing the FPGA is created

### **HDL Synthesis**

### **Technology Mapping**

### **Place & Route**

### **Modern FPGA Development**

}

for (int i = 0; i < SIZE; i++){

c[i] = a[i] \* b[i];</pre>

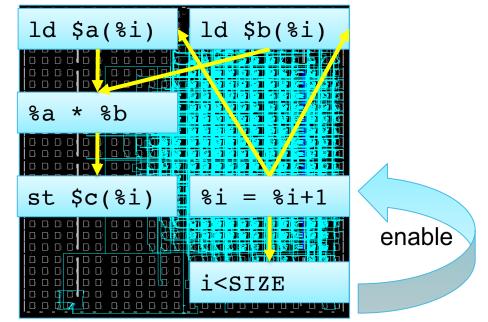

### **Execution on CPU vs on FPGA**

```

for (int i = 0; i < SIZE; i++){

c[i] = a[i] * b[i];

}</pre>

```

#### **Execution on CPU**

• Series of instructions

```

loop:

ld %a $a(%i)

ld %b $b(%i)

%c = %a * %b

st $c(%i) %c

%i = %i + 1

branch i<SIZE: loop</pre>

```

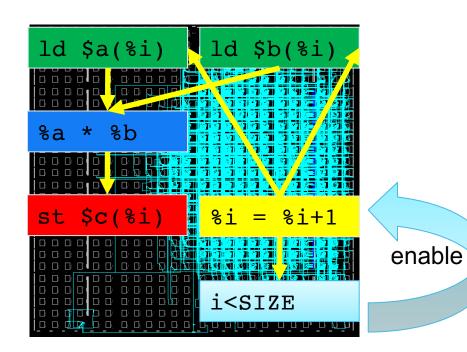

#### **Execution on FPGA**

• Spatial data path + control

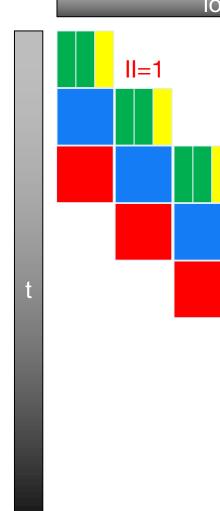

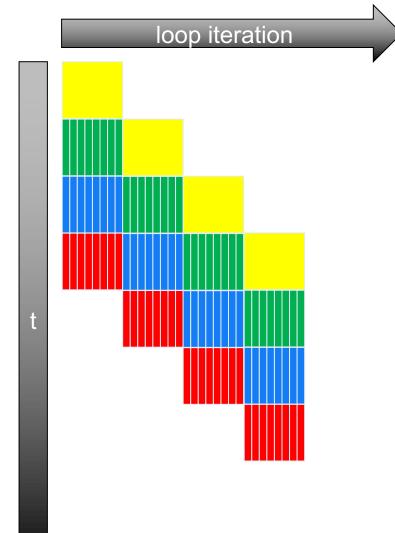

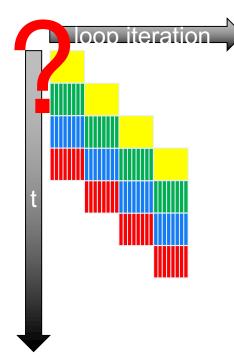

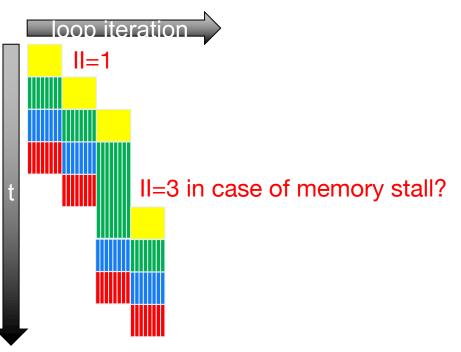

# **Pipelining**

- Use functional units every cycle

- Initiation intervall II

- describes pipeline fill rate

| ld \$a(%i) | ld \$b(%i)                                                                                                                                                                                        |        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|            |                                                                                                                                                                                                   |        |

| %a * %b    | 이이 지하지 이 가지 않고<br>하지 아이가 되어 2 세계 1<br>지하지 아이가 되어 2 세계 1<br>지하지 아이가 아이가 있는 것 같이<br>하지 아이가 아이가 있는 것 같이 같이 하지 않는 것 같이 하는 것 같이 않는 것 같이 있는 것 않 |        |

|            |                                                                                                                                                                                                   |        |

| st \$c(%i) |                                                                                                                                                                                                   |        |

|            |                                                                                                                                                                                                   | enable |

|            | i <size< td=""><td></td></size<>                                                                                                                                                                  |        |

|            |                                                                                                                                                                                                   |        |

#### loop iteration / work item

## **High Level Design Goals**

use (expensive) arithmetic units (almost) every cycle

have scaling designs up to resource or bandwidth limits

- This loop may use

- 2 memory blocks for inputs

- 1 DSP for multiplication

- 1 memory block for output

- 280 logic cells for counter and control

- Could create 3907 instances of this block

- critical resource: 11721 memory blocks / 3

- or 3906 different blocks of this size

- or ...

# **OpenCL** Overview

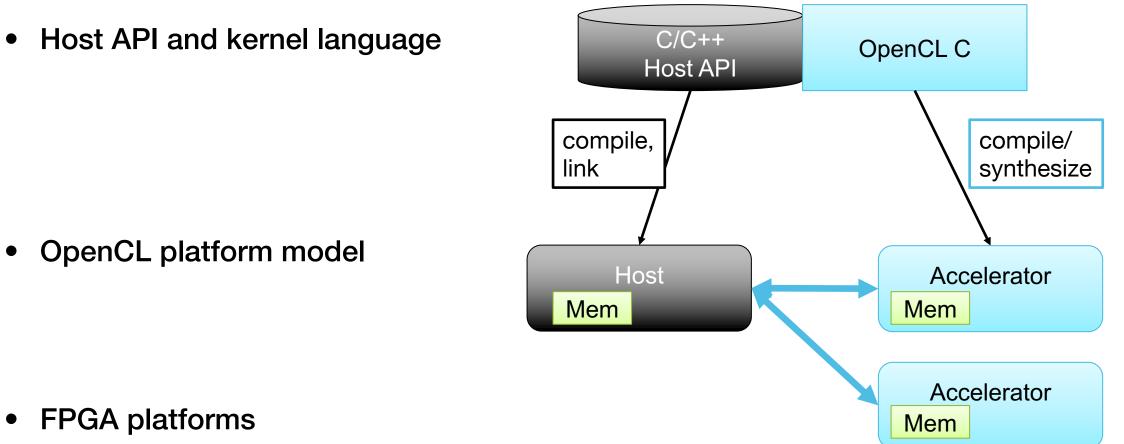

# **OpenCL Standard and Platform Model**

- OpenCL 1.0 standard + selected features

https://www.khronos.org/registry/OpenCL/

### **Host Code**

- Detect a platform ( = runtime library, driver here )

- Detect devices

- Allocate devices ( = create context )

- Create and build program (on FPGA platforms = load and configure bitstreams)

- Create kernel objects

- Create command queues

- Allocate device memory

- Transfer data

- Setup kernel arguments

- Call kernels

- Synchronize

### **Kernel Code**

- Specify accelerator functionality in C syntax

- Special language features

- function qualifier ( \_\_kernel )

- vector data types and operations

- address space qualifiers

- NDRangeKernel concept

- express data parallel execution of work items and work groups

- get\_global\_id

- get\_local\_id

- supported in FPGA platforms, but often not the most efficient method

# **Used Intel OpenCL Platform**

- Intel FPGA SDK for OpenCL 18.1.1

- <u>https://www.intel.com/content/www/us/en/programmable/products/design-software/embedded-software-developers/opencl/support.html</u>

- Release Notes

- Getting Started Guide

- Programming Guide

- Best Practices Guide

- ...

- Download the version specific PDFs!

- Target board: Bittware 520N

- Target FPGA: Intel Stratix 10 GX 2800

- 933120 ALMs

- 11721 M20k memory blocks (20kb each)

- 5760 DSP blocks, 1x 32 bit IEEE 754 SP floating-point or 2x 18x19 multipiers

# **Used Xilinx OpenCL Platform**

- Xilinx SDx 2018.3 SDAccel

- <u>https://www.xilinx.com/html\_docs/xilinx2018\_3/sdaccel\_doc/index.html</u>

- https://www.xilinx.com/products/design-tools/software-zone/sdaccel.html#documentation

- Release Notes, Installation, and Licensing Guide

- Environment User Guide

- SDAccel Environment Programmers Guide

- SDAccel Environment Profiling and Optimization Guide

- SDx Pragma Reference Guide

- ...

- Download the version specific PDFs!

- Target board: Alpha Data ADM-PCIE-8k5

- Target FPGA: Xilinx Kintex Ultrascale KU115-

- 663360 CLB LUTs

- 2160 BRAM blocks, 36kb each

- 5520 DSP slices, 27x18 multipliers

### **Note on Xilinx Tool Scope**

- SDx combines GUI tool and command line compiler for

- SoCs (Zynq) and discrete target platforms (PCle)

- SoCs

- enables shared memory and CPU-FPGA interactions beyond OpenCL platform model

- uses SDSoC license

- discrete platforms

- use BSP following OpenCL platform model

- use SDAccel license

- OpenCL and C/C++ kernel specification

- OpenCL

- attributes can be used to guide high-level synthesis step

- C/C++

- HLS pragmas are used to guide high-level synthesis step (more available)

- fixed kernel interface for discrete target platforms

- Scope in this talk: discrete target platforms with OpenCL

### **Outline Part 1**

- Overview FPGAs and Goals

- OpenCL Overview

- Example 1: Vector Scale

- compilation

- reports

- performance analysis

- Vector Scale Variations

- automatic unrolling

- Example 2: SAXPY

- blockwise design pattern

- Outer Loop Pipelining

- Streaming Kernels

# **Example 1: vector scale**

### **Vector Scale Single-Work Item Kernel**

• Examples and essential reports of both tools available at

https://github.com/kenter/OpenCL-FPGA-examples

```

kernel

void vscale(

global float16 *restrict x,

global float16 *restrict y,

const float a,

const int size16)

{

vscale:

for(int i=0; i<size16; i++){</pre>

y[i] = x[i]*a;

}

```

## **Pipelining: Expectation**

```

kernel

void vscale(

global float8 *restrict x,

global float8 *restrict y,

const float a,

const int size8)

ł

vscale:

for(int i=0; i<size8; i++){</pre>

y[i] = x[i]*a;

}

```

### **Compiling with Intel FPGA SDK for OpenCL**

aoc -rtl -report -v -board=p520\_max\_sg2801 -fp-relaxed -fpc device/vscale1\_vec.cl

[[kenter@fe-1 examples]\$ make reportIntel-vscale1\_vec aoc -rtl -report -v -board=p520\_max\_sg280l -fp-relaxed -fpc device/vscale1\_vec.cl aoc: Environment checks are completed successfully. aoc: Cached files in /var/tmp/aocl/ may be used to reduce compilation time aoc: Selected target board p520\_max\_sg280l aoc: Running OpenCL parser.... aoc: OpenCL parser completed successfully. aoc: Linking Object files.... aoc: Optimizing and doing static analysis of code... aoc: Linking with IP library ... Checking if memory usage is larger than 100%

| Estimated Resource Usage Summary | +       |  |

|----------------------------------|---------|--|

| Resource                         | + Usage |  |

| Logic utilization                | ; 69%   |  |

| ALUTS                            | ; 36%   |  |

| Dedicated logic registers        | ; 36%   |  |

| Memory blocks                    | ; 32%   |  |

| DSP blocks                       | : 29%   |  |

# Intel Report (1) Summary

- reports/report.html

- Summary

- 1 Single work-item kernel

- high resource includes BSP

| Info                                                                                                                            |                                                                  |                                                 |                                       |                  |                           |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------|---------------------------------------|------------------|---------------------------|

| Project Name                                                                                                                    | vscale1_v                                                        | ec                                              |                                       |                  |                           |

| Target Family, Device, Bo                                                                                                       | oard Stratix 10                                                  | , 1SG280LU3F50E1                                | /GS1, nalla_pcie:                     | p520_max_sg2     | BOL                       |

| AOC Version                                                                                                                     | 18.1.1 Bui                                                       | ild 263                                         |                                       |                  |                           |

| Quartus Version                                                                                                                 | 18.1.1 Bui                                                       | ld 263 Pro                                      |                                       |                  |                           |

| Command                                                                                                                         |                                                                  | eport -v -board=p52<br>cale1_vec.cl             | 0_max_sg280l -                        | fp-relaxed -fpc  |                           |

| Reports Generated At                                                                                                            | Fri Mar 22                                                       | 13:52:36 2019                                   |                                       |                  |                           |

| Quartus Fit Summa                                                                                                               | ary                                                              |                                                 |                                       |                  |                           |

|                                                                                                                                 |                                                                  | C                                               | va information                        |                  |                           |

| Run Quartus compile to                                                                                                          | o populate this sectio                                           | n. See details for mo                           | ore information.                      |                  |                           |

|                                                                                                                                 |                                                                  | n, See details for mo                           |                                       | HyperFlex        |                           |

| Kernel Summary<br>Kernel Name Kernel 7                                                                                          | Type Autorur                                                     | n Workgroup Size                                | # Compute Ur                          | Control O        | x<br>ptimizatior          |

| Kernel Summary<br>Kernel Name Kernel 7                                                                                          |                                                                  |                                                 |                                       | aite             |                           |

| Kernel Summary<br>Kernel Name Kernel T<br>vscale Single w                                                                       | Type Autorur<br>vork-item No                                     | n Workgroup Size                                | # Compute Ur                          | Control O        |                           |

| Kernel Summary<br>Kernel Name Kernel T<br>vscale Single w                                                                       | Type Autorur<br>vork-item No                                     | n Workgroup Size                                | # Compute Ur                          | Control O        |                           |

| Kernel Summary<br>Kernel Name Kernel 7<br>vscale Single w<br>Estimated Resource                                                 | Type Autorur<br>vork-item No<br>e Usage                          | 1 Workgroup Size                                | # Compute Ur<br>1                     | On               | ptimizatior               |

| Kernel Summary<br>Kernel Name Kernel T<br>vscale Single w<br>Estimated Resource<br>Kernel Name                                  | Type Autorur<br>vork-item No<br>e Usage<br>ALUTs                 | 1 Workgroup Size<br>1,1,1<br>FFs                | # Compute Ur<br>1<br>RAMs             | On<br>On<br>DSPs | ptimizatior<br>MLABs      |

| Kernel Summary<br>Kernel Name Kernel T<br>vscale Single w<br>Estimated Resource<br>Kernel Name<br>vscale                        | Type Autorur<br>vork-item No<br>e Usage<br>ALUTs<br>3846         | Workgroup Size<br>1,1,1<br>FFs<br>9482          | # Compute Ur<br>1<br>RAMs<br>46       | On<br>On<br>DSPs | ptimization<br>MLABs<br>8 |

| Kernel Summary<br>Kernel Name Kernel T<br>vscale Single w<br>Estimated Resource<br>Kernel Name<br>vscale<br>Global Interconnect | Type Autorur<br>vork-item No<br>e Usage<br>ALUTs<br>3846<br>7490 | Workgroup Size<br>1,1,1<br>FFs<br>9482<br>15614 | # Compute Ur<br>1<br>RAMs<br>46<br>52 | DSPs<br>0        | MLABs<br>8<br>0           |

| sca  | e1_vec.cl •                                               | ×     |

|------|-----------------------------------------------------------|-------|

| 1    | <pre>#include "macros.h"</pre>                            |       |

| 2    | · · · · · · · · · · · · · · · · · · ·                     |       |

| 3    | kernel                                                    |       |

| 4    | void vscale(                                              |       |

| 5    | global float16 *restrict x,                               |       |

| 6    | global float16 *restrict y,                               |       |

| 7    | const float a,                                            |       |

| 8    | const int size)                                           |       |

| 9 -  |                                                           |       |

| 10   | vscale:                                                   |       |

| 11   | <pre>//attribute((xcl_pipeline_loop(</pre>                | (1))) |

| 12 - | <pre>for(int i=0; i<size; i++){<="" pre=""></size;></pre> |       |

| 13   | y[i] = x[i]*a;                                            |       |

| 14   | }                                                         |       |

| 15   | }                                                         |       |

| 16   |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

|      |                                                           |       |

# Intel Report (2) Loop Analysis

• Loop analysis

| Loops analysis                    | lysis     |    | Show full  | y unrolled loops        |

|-----------------------------------|-----------|----|------------|-------------------------|

|                                   | Pipelined | н  | Bottleneck | Details                 |

| Kernel: vscale (vscale1_vec.cl:4) |           |    |            | Single work-item ex     |

| vscale.B2 (vscale1_vec.cl:12)     | Yes       | ~1 | n/a        | II is an approximation. |

#### vscale.B2:

- Loop orchestration compiler optimization is enabled.

- Il is an approximation due to the following stallable instructions:

- Load Operation (vscale1\_vec.cl: 13)

- Store Operation (vscale1\_vec.cl: 13)

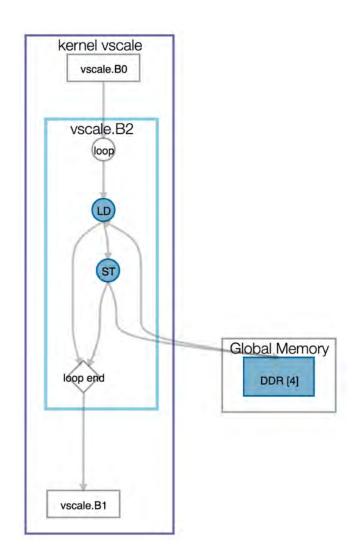

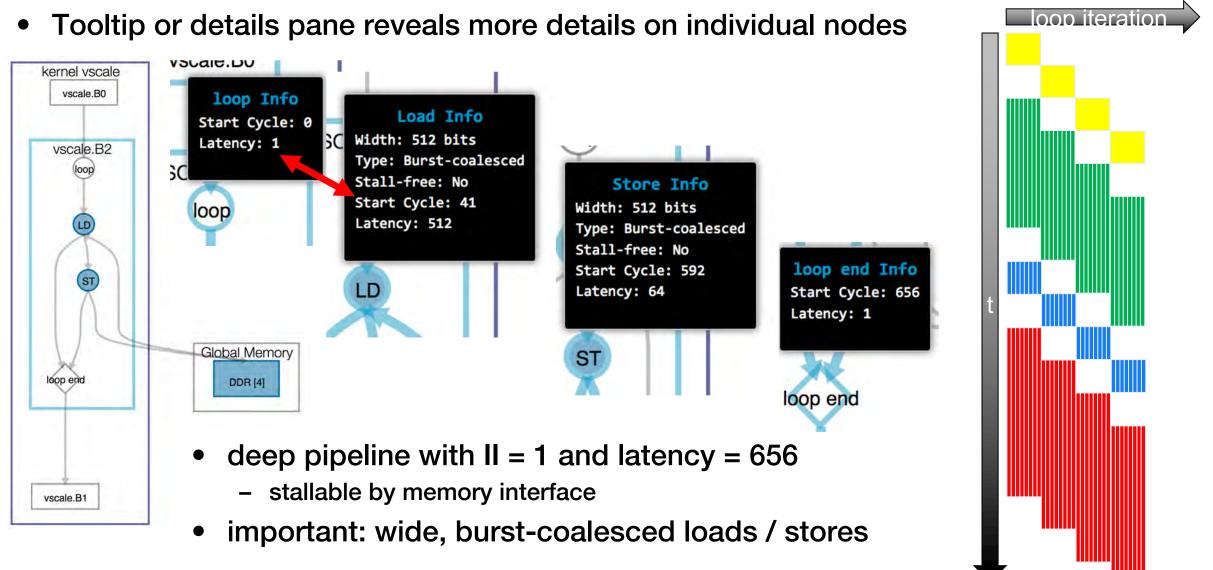

### Intel Report (3) System viewer

| <ul> <li>System viewer</li> </ul> | • |

|-----------------------------------|---|

|-----------------------------------|---|

- selecting the loop denoted as vsacle.B2

| Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| vscale.B2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 656 |

| II Contraction of the second sec | 1   |

| Subloops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No  |

| Pipelined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Yes |

| Fmax Bottlenecks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No  |

| Loop Info                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

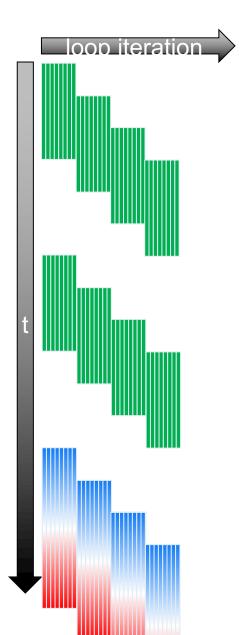

# **Pipeline Following System Viewer**

## Intel Report (4) Area Analysis

| Notation file:X > file:Y indica                | ates a function o | all on line X w | as inlined usi | ing code on l | line Y. |                                                  | 1 #include "macros.h"<br>2<br>3kernel                           |

|------------------------------------------------|-------------------|-----------------|----------------|---------------|---------|--------------------------------------------------|-----------------------------------------------------------------|

|                                                | ALUTs             | FFs             | RAMs           | DSPs          | MLABs   | Details                                          | <pre>4 void vscale( 5global float16 *restrict x,</pre>          |

| Static Partition                               | 480580 (35%)      | 961160 (35%)    | 2766 (31%)     | 1292 (29%)    | 0 (0%)  |                                                  | <pre>6global float16 *restrict y,<br/>7 const float a,</pre>    |

| Kernel System                                  | 11338 (1%)        | 25167 (1%)      | 100 (1%)       | 16 (0%)       | 8 (0%)  |                                                  | <pre>8 const int size) 9 - {</pre>                              |

| Global interconnect                            | 7490              | 15614           | 52             | 0             | 0       | For 1 global load a                              | <pre>10 vscale:<br/>11 //attribute((xcl_pipeline_loop(1))</pre> |

| System description ROM                         | 2                 | 71              | 2              | 0             | 0       | Contains informati                               | 12 * for(int i=0; i <size; i++){<br="">13</size;>               |

| ♥ vscale                                       | 3846 (0%)         | 9482 (0%)       | 46 (1%)        | 16 (0%)       | B (0%)  | 1 compute unit.                                  | 14 }<br>15 }                                                    |

| Function overhead                              | 1463              | 1467            | 0              | 0             | 6       | Kernel dispatch lo                               | 16                                                              |

| Private Variable:<br>- 'i' (vscale1_vec.cl:12) | 32                | 130             | 0              | 0             | 0       | Register,<br>1 reg, 32 width,<br>1 reg, 33 width |                                                                 |

| > vscale.B0                                    | 191 (0%)          | 144 (0%)        | 0 (0%)         | 0 (0%)        | 1 (0%)  |                                                  |                                                                 |

| ♥ vscale.B2                                    | 2160 (0%)         | 7741 (0%)       | 46 (1%)        | 16 (0%)       | 1 (0%)  |                                                  |                                                                 |

| Cluster logic                                  | 418               | 722             | 16             | 0             | 1       | Logic required to e                              |                                                                 |

| > State                                        | 34                | 697             | 1              | 0             | 0       | Live values and co                               |                                                                 |

| > Feedback                                     | 65                | 41              | 0              | 0             | 0       | Loop-carried depe                                |                                                                 |

| ✓ Computation                                  | 1643              | 6281            | 29             | 16            | 0       |                                                  |                                                                 |

| vscale1_vec.cl:12                              | 105               | 0               | 0              | 0             | 0       |                                                  |                                                                 |

| > vscale1_vec.cl:13                            | 1538              | 6281            | 29             | 16            | 0       |                                                  |                                                                 |

• 16 DSPs for 16 float multiplications

## **Design Review (1)**

#### use (expensive) arithmetic units (almost) every cycle

have scaling designs up to resource or bandwidth limits

- Initiation Intervall II = 1

- Latency L = 656

- Iterations N

- Time in Cycles C = N x II + L

| Ν      | С      | Efficiency |

|--------|--------|------------|

| 10     | 666    | 1.5%       |

| 100    | 756    | 13.2%      |

| 1000   | 1656   | 60.4%      |

| 10000  | 10656  | 93.8%      |

| 100000 | 100656 | 99.3%      |

## **Design Review (2)**

#### use (expensive) arithmetic units (almost) every cycle

#### have scaling designs up to resource or bandwidth limits

- Read and write 16 floats (32 bit) per cycle

- $-2 \times 512$  bit = 2 x 64 byte per cycle

- Peak bandwidth of board

- 4 x (64+8) bit x 2400 MHz (physical interface)

- 4 x 512 bit x 300 MHz (OpenCL interface)

- can unroll 2x more or have 2 compute units

- Kernel can run at > 300 MHz (350-400 MHz for this type of simple kernel)

- 2x unrolled version mildly bandwidth limited

- Main problem: low arithmetic intensity

- only 16 of 5760 DSPs used 0.28% utilization 0.55% with another 2x unrolling

#### **Compiling with Xilinx SDx (SDAccel)**

xocc -g -R 2 -s --platform=alpha-data\_adm-pcie-8k5\_dynamic\_5\_0

--memory\_port\_data\_width all:512 -c device/vscale1\_vec.cl -o

vscale1 vec.xo

[kenter@fe-1 examples]\$ make reportXilinx-vscale1\_vec make: aocl: Command not found make: aocl: Command not found xocc -g -R 2 -s --platform=alpha-data\_adm-pcie-8k5\_dynamic\_5\_0 --memory\_port\_data\_width all:512 -c device/vscale1\_vec.cl -o vscale1\_vec.xo

\*\*\*\*\*\* xocc v2018.3 (64-bit)

\*\*\*\* SW Build 2405991 on Thu Dec 6 23:36:41 MST 2018

\*\* Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

Attempting to get a license: ap\_opencl

INFO: [XOCC 60-1306] Additional information associated with this xocc compile can be found at: Reports: /upb/scratch/departments/pc2/groups/pc2-mitarbeiter/kenter/gitlab/2019-date-tutorial/examples/\_x/reports/vscale1\_vec Log files: /upb/scratch/departments/pc2/groups/pc2-mitarbeiter/kenter/gitlab/2019-date-tutorial/examples/\_x/logs/vscale1\_vec INFO: [XOCC 60-585] Compiling for hardware target Running SDx Rule Check Server on port:36586 INFO: [XOCC 60-895] Target platform: /opt/Xilinx/SDx/2018.3/platforms/alpha-data\_adm-pcie-8k5\_dynamic\_5\_0/alpha-data\_adm-pcie-8k5\_dynamic\_5\_0.xpfm INFO: [XOCC 60-423] Target device: alpha-data\_adm-pcie-8k5\_dynamic\_5\_0

===>The following messages were generated while performing high-level synthesis for kernel: vscale Log file: /upb/scratch/departments/pc2/groups/pc2-mita rbeiter/kenter/gitlab/2019-date-tutorial/examples/\_x/vscale1\_vec/vscale/vivado\_hls.log :

INFO: [XOCC 204-6] Pipelining loop 'vscale'. INFO: [XOCC 204-6] Pipelining result : Target II = 1, Final II = 1, Depth = 10. INFO: [XOCC 60-50] Finished kernel compilation

INFO: [XOCC 60-244] Generating system estimate report...

INFO: [XOCC 60-1092] Generated system estimate report: /upb/scratch/departments/pc2/groups/pc2-mitarbeiter/kenter/gitlab/2019-date-tutorial/examples/\_x/re ports/vscale1\_vec/system\_estimate\_vscale1\_vec.xtxt

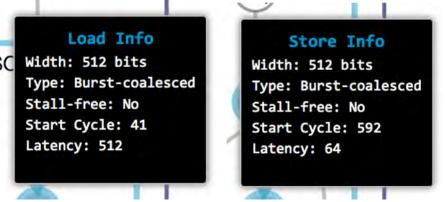

## Xilinx Report (1) Vivado HLS Log

#### • Vivado HLS log

38 INFO: [HLS 214-115] Burst read of variable length and width 512 has been inferred on 'gmem' (/upb/scratch/ departments/pc2/groups/pc2-mitarbeiter/kenter/gitlab/2019-date-tutorial/examples/device/vscale1\_vec.cl:12:5)

39 INFO: [HLS 214-115] Burst write of variable length and width 512 has been inferred on 'gmem' (/upb/scratch/ departments/pc2/groups/pc2-mitarbeiter/kenter/gitlab/2019-date-tutorial/examples/device/vscale1\_vec.cl:12:5)

#### • Similar 512 bit burst loads / stores

| 53 INFO: [HLS 200-10]                                                        |           |

|------------------------------------------------------------------------------|-----------|

| 54 INF0: [SCHED 204–11] Starting scheduling                                  |           |

| 55 INFO: [SCHED 204-61] Pipelining loop 'vscale'.                            |           |

| 56 INFO: [SCHED 204-61] Pipelining result : Target II = 1, Final II = 1, Dep | oth = 10. |

- II = 1

- Depth = 10 vs. Latency = 656 in Intel Design

- different terminology, different treatment of off-chip memory latency

- latency is still there (will see in next example) estimate of loop efficiency harder

### Xilinx Report (2) System Estimate

#### • System estimate

| 35 | Area Informat | ion         |             |      |      |     |      |

|----|---------------|-------------|-------------|------|------|-----|------|

| 36 | Compute Unit  | Kernel Name | Module Name | FF   | LUT  | DSP | BRAM |

| 37 |               |             |             |      |      |     |      |

| 38 | vscale_1      | vscale      | vscale      | 6213 | 4806 | 48  | 30   |

| 39 |               |             |             |      |      |     |      |

- 3 DSPs (+ some logic) per MUL

- need to combine 27x18 multipliers

- Vivado HLS provides some control over balance between DSPs and logic

- SDx with OpenCL inputs not directly

- short multiplications can be done with single DSP

```

xocc -g -R 2 -s --platform=alpha-data_adm-pcie-8k5_dynamic_5_0 --memory_port_data_width all:256

-c device/vscale5_short.cl -o vscale5_short.xo

```

| 35 | Area Informat | 10n         |             |      |      |     |      |

|----|---------------|-------------|-------------|------|------|-----|------|

| 36 | Compute Unit  | Kernel Name | Module Name | FF   | LUT  | DSP | BRAM |

| 37 |               |             |             |      |      |     |      |

| 38 | vscale_1      | vscale      | vscale      | 1982 | 2273 | 16  | 16   |

| 39 |               |             |             |      |      |     |      |

#### **Vector Scale Summary**

- 2 very similar designs

- Found pipelining in reports

- Found 512 bit wide burst-coalesced loads / stores in reports

- Found 16 parallel floating point MULs indirectly in resource estimate

use (expensive) arithmetic units (almost) every cycle

have scaling designs up to resource or **bandwidth** limits

• It's much easier to reach bandwidth limits than compute resource limits

## **Vector Scale Variations**

#### **Vector Scale with Unrolling**

```

kernel

void vscale(

global float *restrict x,

global float *restrict y,

const float a,

const int size)

{

attribute ((opencl_unroll_hint(16)))

for(int i=0; i<size; i++){</pre>

y[i] = x[i]*a;

}

```

More typical alternative for Intel compiler #pragma unroll 16

- <u>https://github.com/kenter/OpenCL-FPGA-examples</u> -> vscale2\_u.cl

- report files in reportIntel and reportXilinx

- What has changed in contrast to vscale1\_vec (throughput, resources, ...)?

## **Intel Report: Area Analysis**

| Area analysis of system<br>(area utilization values are e<br>Notation <i>file:X</i> > <i>file:Y</i> indica |              | call on line X w | as inlined usi | Area analysis of system<br>(area utilization values are<br>Notation <i>file:X</i> > <i>file:Y</i> indi | and the second of the second second | call on line X v | was inlined u | sing code on |         | Collapse All                 |

|------------------------------------------------------------------------------------------------------------|--------------|------------------|----------------|--------------------------------------------------------------------------------------------------------|-------------------------------------|------------------|---------------|--------------|---------|------------------------------|

|                                                                                                            | ALUTs        | FFs              | RAMs           |                                                                                                        | ALUTs                               | FFs              | RAMs          | DSPs         | MLABs   | Details                      |

| Static Partition                                                                                           | 480580 (35%) | 961160 (35%)     | 2766 (31%)     | > Static Partition                                                                                     | 480580 (35%)                        | 961160 (35%)     | 2766 (31%)    | 1292 (29%)   | 0 (0%)  |                              |

| ✓ Kernel System                                                                                            | 11338 (1%)   | 25167 (1%)       | 100 (1%)       | ♥ Kernel System                                                                                        | 12134 (1%)                          | 25559 (1%)       | 105 (1%)      | 16 (0%)      | 12 (0%) |                              |

| Global interconnect                                                                                        | 7490         | 15614            | 52             | Global interconnect                                                                                    | 7490                                | 15614            | 52            | 0            | 0       | For 1 global load a          |

| System description ROM                                                                                     | 2            | 71               | 2              | System description ROM                                                                                 | 2                                   | 71               | 2             | 0            | 0       | Contains informati           |

| ♥ vscale                                                                                                   | 3846 (0%)    | 9482 (0%)        | 46 (1%)        | ♥ vscale                                                                                               | 4642 (0%)                           | 9874 (0%)        | 51 (1%)       | 16 (0%)      | 12 (0%) | 1 compute unit.              |

| Function overhead                                                                                          | 1463         | 1467             | 0              | Function overhead                                                                                      | 1463                                | 1467             | 0             | 0            | 6       | Kernel dispatch lo           |

| Private Variable:<br>- 'i' (vscale1_vec.cl:12)                                                             | 32           | 130              | 0              | Private Variable:<br>- 'i' (vscale2_u.cl:12)                                                           | 24                                  | 64               | 0             | 0            | 0       | Register,<br>1 reg, 32 width |

| > vscale.B0                                                                                                | 191 (0%)     | 144 (0%)         | 0 (0%)         | > vscale.B0                                                                                            | 59 (0%)                             | 75 (0%)          | 0 (0%)        | 0 (0%)       | 1 (0%)  |                              |

| ♥ vscale.B2                                                                                                | 2160 (0%)    | 7741 (0%)        | 46 (1%)        | ♥ vscale.B1                                                                                            | 3096 (0%)                           | 8268 (0%)        | 51 (1%)       | 16 (0%)      | 5 (0%)  |                              |

| Cluster logic                                                                                              | 418          | 722              | 16             | Cluster logic                                                                                          | 497                                 | 865              | 20            | 0            | 1       | Logic required to e          |

| > State                                                                                                    | 34           | 697              | 1              | > State                                                                                                | 92                                  | 972              | 2             | 0            | 4       | Live values and co           |

| > Feedback                                                                                                 | 65           | 41               | 0              | > Feedback                                                                                             | 48                                  | 41               | 0             | 0            | 0       | Loop-carried depe            |

| ✓ Computation                                                                                              | 1643         | 6281             | 29             | ✓ Computation                                                                                          | 2459                                | 6390             | 29            | 16           | 0       |                              |

| > vscale1_vec.cl:12                                                                                        | 105          | 0                | 0              | > No Source Line                                                                                       | 256                                 | 64               | 0             | 0            | 0       |                              |

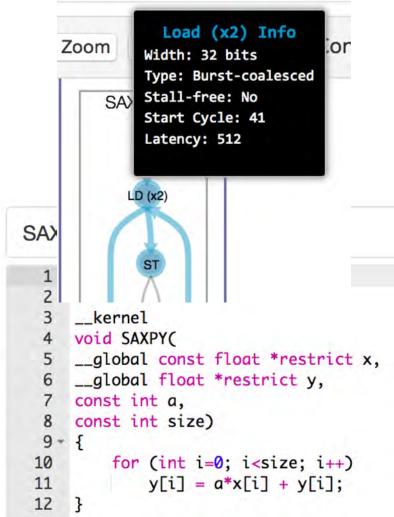

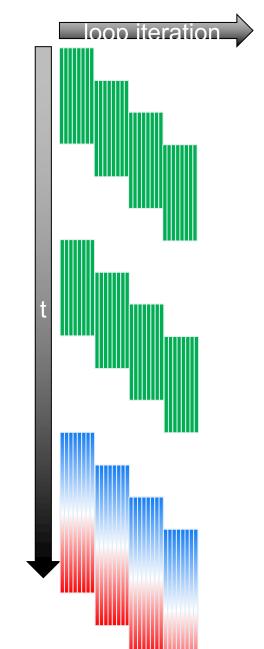

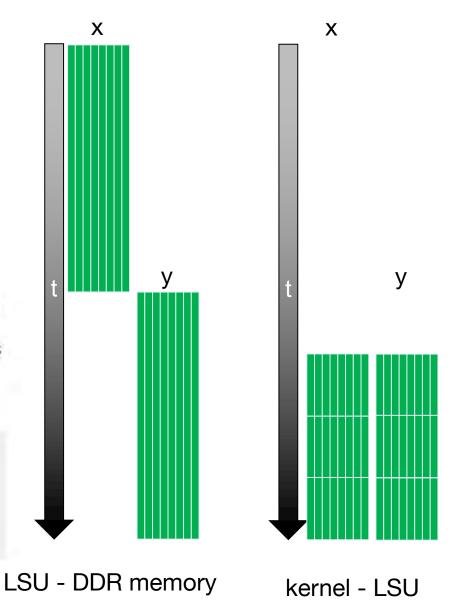

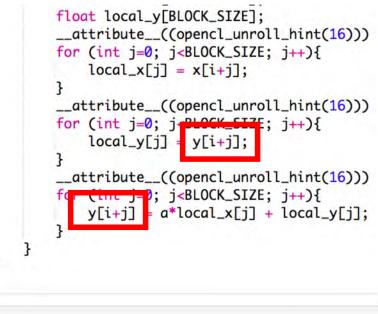

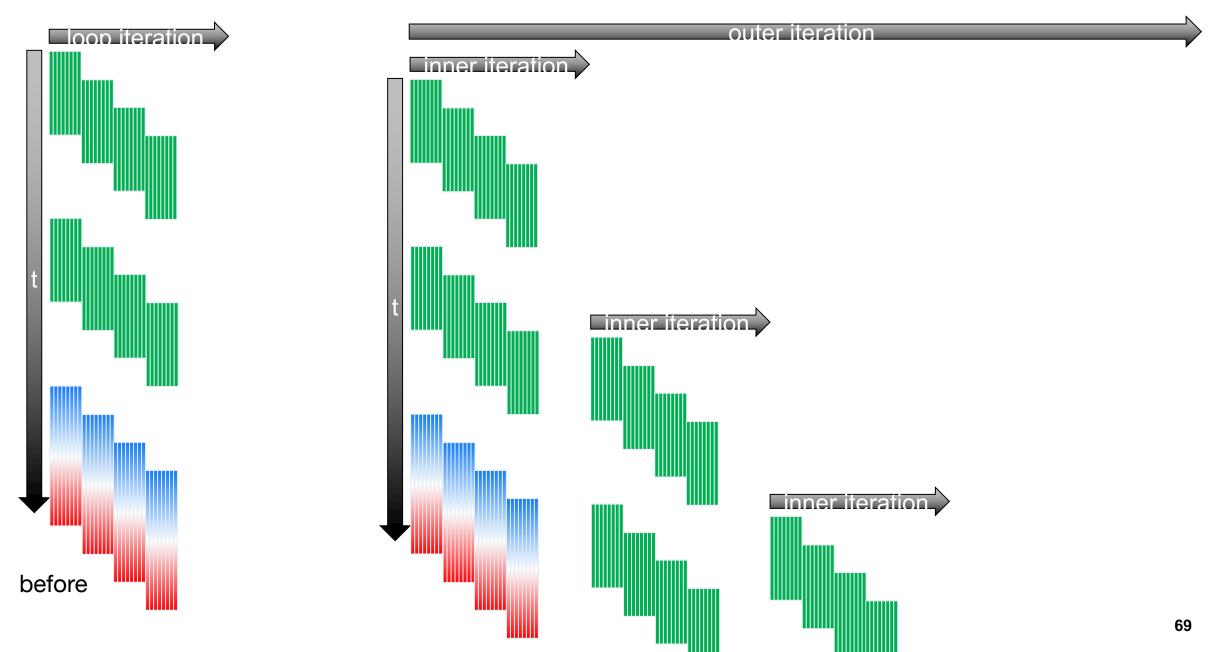

| > vscale1_vec.cl:13                                                                                        | 1538         | 6281             | 29             | > vscale2_u.cl:12                                                                                      | 664                                 | 44               | 0             | 0            | 0       |                              |