Programmable Programs? - Designing FPGA overlay architectures with OpenCL

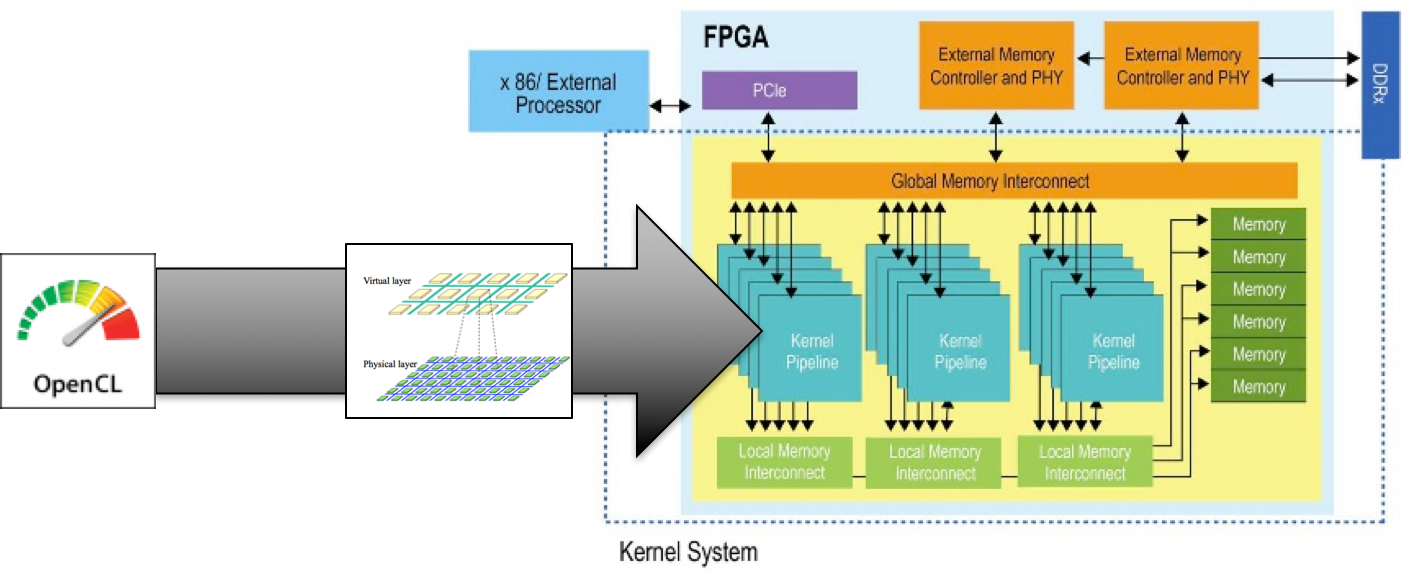

FPGAs allow to accelerate a wide range of applications by customizing the hardware to the required compute and data access patterns. However, they are traditionally difficult to program and require time-consuming synthesis processes. Both challenges can be met with overlay architectures, which provide an abstraction layer on top of the original FPGA fabric. Structurally programmable overlays exhibit operators and connections for entire data words instead of individual bits, whereas soft processors can be programmed by instructions using ordinary compilers. But how can we efficiently design customizable overlays?

New design flows around OpenCL have been adopted by both big FPGA vendors, Xilinx and Altera, and we have both hardware and software available. In this thesis you will explore, how OpenCL can be used to design either a soft processor or a structured dataflow overlay and demonstrate its functionality and performance compared to direct hardware implementations with OpenCL.

Tasks

- Implement with OpenCL a programmable FPGA overlay

- Soft processor or array structure

- Demonstrate functionality with simple kernels

- Compare to direct OpenCL-to-FPGA implementations

Recommended Skills

- Experience/Interest in OpenCL or other accelerator languages

- Interest in computer architecture + novel computing paradigms